Electrical Extraction

Icon:

Dock: Extraction

Description

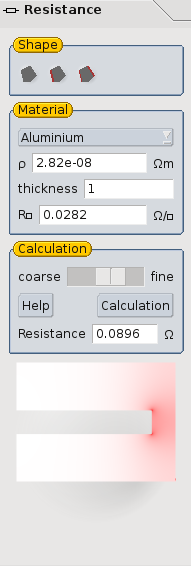

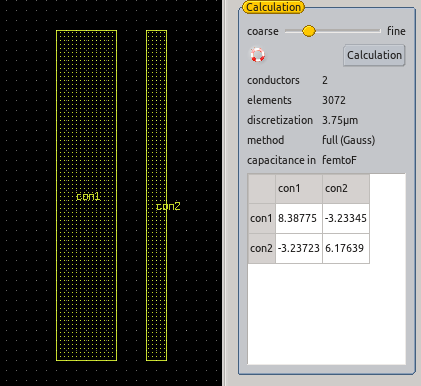

The LayoutEditor includes a complete extraction tool set for most common application. There is an easy-to-operate user interface for fast extraction of simple electrical parameters such as resistance, capacitance or inductance. After calling up one of the simple extraction tools, a dock window will open with features that extract electrical properties from the design. The window includes extraction of resistance per a single arbitrary shape for direct current, a three dimensional capacitance extraction using the FastCap algorithm and inductance extraction using the FastHenry algorithm. Please see the individual sections for details about how to use:

Along with the simple extraction methods via graphical user interface, there are several other device extraction procedures available. These extraction methods are defined in the component library and triggered manually by a button in the extraction windows or by macros. All detected devices will be defined in a way, that an extracted netlist in any supported format can be created and the created netlist can be used for design validation. Supported extraction methods are available for MOS-transistors, bipolar transistors, capacitance to ground, parallel plate capacitance and determining the resistance of any arbitrary shape with multi connectors. For a complete description, please see:

Example

See also

CategoryFeature CategoryFullVersion CategoryLayout CategoryUtilityMenu FeatureCode:1282